湖南陶瓷封装方案

系统级封装的优势,SiP和SoC之间的主要区别在于,SoC 将所需的每个组件集成到同一芯片上,而 SiP方法采用异构组件并将它们连接到一个或多个芯片载波封装中。例如,SoC将CPU,GPU,内存接口,HDD和USB连接,RAM / ROM和/或其控制器集成到单个芯片上,然后将其封装到单个芯片中。相比之下,等效的SiP将采用来自不同工艺节点(CMOS,SiGe,功率器件)的单独芯片,将它们连接并组合成单个封装到单个基板(PCB)上。考虑到这一点,很容易看出,与类似的SoC相比,SiP的集成度较低,因此SiP的采用速度很慢。然而,较近,2.5D 和 3D IC、倒装芯片技术和封装技术的进步为使用 SiP 提供的可能性提供了新的视角。有几个主要因素推动了当前用SiP取代SoC的趋势:SiP 可以将多个具有不同功能的有源电子元件与可选无源器件。湖南陶瓷封装方案

2.5D SIP,2.5D本身是一种在客观世界并不存在的维度,因为其集成密度超越了2D,但又达不到3D集成密度,取其折中,因此被称为2.5D。其中的表示技术包括英特尔的EMIB、台积电的CoWos、三星的I-Cube。在先进封装领域,2.5D是特指采用了中介层(interposer)的集成方式,中介层目前多采用硅材料,利用其成熟的工艺和高密度互连的特性。物理结构:所有芯片和无源器件均在XY平面上方,至少有部分芯片和无源器件安装在中介层上,在XY平面的上方有中介层的布线和过孔,在XY平面的下方有基板的布线和过孔。电气连接:中介层可提供位于中介层上芯片的电气连接。虽然理论上讲,中介层可以有TSV也可以没有TSV,但在进行高密度互连时,TSV几乎是不可或缺的,中介层中的TSV通常被称为2.5D TSV。湖南系统级封装流程SiP并没有一定的结构形态,芯片的排列方式可为平面式2D装和立体式3D封装。

随着物联网时代越来越深入人心,不断的开发和研究有助于使SiP更接近SoC,降低成本,减少批量要求和初始投资,并在系统简化方面呈现积极趋势。此外,制造越来越大的单片SoC的推动力开始在设计验证和可制造性方面遇到障碍,因为拥有更大的芯片会导致更大的故障概率,从而造成更大的硅晶圆损失。从IP方面来看,SiP是SoC的未来替代品,因为它们可以集成较新的标准和协议,而无需重新设计。此外,SiP方法允许更快、更节能的通信和电力输送,这是在考虑Si应用的长期前景时另一个令人鼓舞的因素。

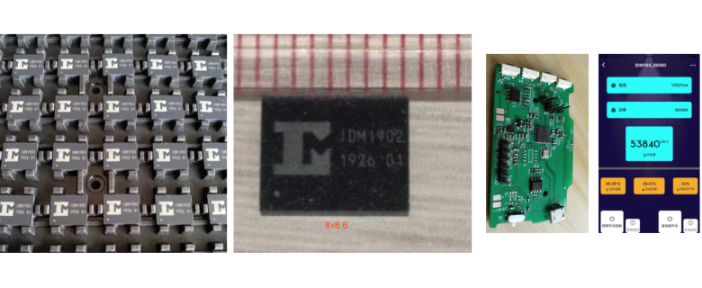

合封电子、芯片合封和SiP系统级封装经常被提及的概念。但它们是三种不同的技术,还是同一种技术的不同称呼?本文将帮助我们更好地理解它们的差异。合封电子与SiP系统级封装的定义,首先合封电子和芯片合封都是一个意思合封电子是一种将多个芯片(多样选择)或不同的功能的电子模块(LDO、充电芯片、射频芯片、mos管)封装在一起的定制化芯片,从而形成一个系统或者子系统。以实现更复杂、更高效的任务。云茂电子可定制组成方式包括CoC封装技术、SiP封装技术等。SiP技术是一项先进的系统集成和封装技术,与其它封装技术相比较,SiP技术具有一系列独特的技术优势。

SiP整体制程囊括了着晶、打线、主/被动组件SMT及塑封技术,封装成型可依据客户设计制作不同形状模块,甚至是3D立体结构,藉此可将整体尺寸缩小,预留更大空间放置电池,提供更大电力储存,延长产品使用时间,但功能更多、速度更快,因此特别适用于射频相关应用如5G毫米波模块、穿戴式装置及汽车电子等领域。微小化制程三大关键技术,在设计中元器件的数量多寡及排布间距,即是影响模块尺寸的较主要关键。要能够实现微小化,较重要的莫过于三项制程技术:塑封、屏蔽及高密度打件技术。随着SiP模块成本的降低,且制造工艺效率和成熟度的提高。天津系统级封装流程

在固晶过程中,需要对芯片施加一定的压力以确保其与基板之间的良好连接。湖南陶瓷封装方案

包装,主要目的是保证运输过程中的产品安全,及长期存放时的产品可靠性。对包装材料的强度、重量、温湿度特性、抗静电性能都有一定的要求。主要材料有Tray盘,抗静电袋,干燥剂、湿度卡,纸箱等。包装完毕后,直接入库或按照要求装箱后直接发货给客户。倒装焊封装工艺工序介绍,焊盘再分布,为了增加引线间距并满足倒装焊工艺的要求,需要对芯片的引线进行再分布。制作凸点,焊盘再分布完成之后,需要在芯片上的焊盘添加凸点,焊料凸点制作技术可采用电镀法、化学镀法、蒸发法、置球法和焊膏印尽4法。目前仍以电镀法较为普遍,其次是焊膏印刷法。湖南陶瓷封装方案

上一篇: 江西专业电子产品方案市价