惠州圆形集成电路测试

在一些实施例中,调节访问装置可以包括与工作mtj器件并联连接的薄膜电阻器和薄膜电阻器。在各个实施例中,调节访问装置可以包括具有基本类似的尺寸或具有不同的尺寸的电阻器。存储器阵列通过多条位线bl至bl和多条字线wl至wl连接至控制电路。在一些实施例中,控制电路包括连接至多条位线bl至bl的位线解码器和连接至多条字线wl至wl的字线解码器。调节访问装置连接在字线wlx(x=或)和工作mtj器件之间,而工作mtj器件连接在调节访问装置和位线bly(y=或)之间。为了访问工作mtj器件。位线解码器被配置为基于从控制单元接收的地址saddr选择性地向一条或多条位线bl至bl提供信号(例如,电压)。而字线解码器被配置为基于从控制单元接收的地址saddr选择性地向一条或多条字线wl至wl提供信号(例如,电压)。调节访问装置被配置为调节电流(提供给相关的工作mtj器件的信号),并且由此选择性地对相关的工作mtj器件提供访问。例如,在写入操作期间,存储器阵列内的调节访问装置可以对选择的存储单元内的工作mtj器件提供大于或等于小切换电流(即,足以使存储单元的数据状态改变的电流)电流,而对未选择的存储单元内的工作mtj器件提供小于小切换电流的电流。这些年来,集成电路持续向更小的外型尺寸发展,使得每个芯片可以封装更多的电路。惠州圆形集成电路测试

下基板2的上层金属层9、下层金属层10通孔沉金19、20,用于中间填充层的21,上基板1中间层22、下基板2中间层23。图2示出依据本申请一实施例的双芯片集成电路封装结构201,包括上基板1、元件3、元件4及下基板2,上基板1上的上层金属层5、下层金属层6以及下层金属层6上的联结pad7、8、9、10,下基板2上的上层金属层11、下层金属层12以及上层金属层11上的pad13、14、15、16,下层金属层12上的联结pad17、18、19、20、21、联结pad22。上基板1与下基板2联结用的沉金23、24,下基板2的上层金属层11、下层金属层12通孔沉金25、26、27、28,用于中间填充层的29,上基板1中间层30、下基板2中间层31。以上所述实施例用以说明本申请的技术方案,而非对其限制;尽管参照前述实施例对本申请进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型各实施例技术方案的精神和范围,均应包含在本申请的保护范围之内。中规模集成电路公司集成电路的分类方法依照电路属模拟,可以分为:模拟集成电路、数字集成电路和混合信号集成电路.

在一些实施例中,固定层可以包括钴(co)、铁(fe)、硼(b)、镍(ni)、钌(ru)、铱(ir)、铂(pt)等。在一些实施例中,介电遂穿阻挡层可以包括氧化镁(mgo)、氧化铝(alo)等。在一些实施例中,自由层可以包括钴(co)、铁(fe)、硼(b)等。在操作期间。字线解码器被配置为选择性地将信号施加至连接至存储器阵列的一条或多条字线wl至wl,并且位线解码器被配置成选择性地将信号施加至连接至存储器阵列的一条或多条位线bl至bl。通过选择性地将信号施加至一条或多条字线wl至wl和一条或多条位线bl至bl,可以在相互排斥的情况下选择性地访问多个工作mtj器件中的不同工作mtj器件。例如,图a至图b示出了图的存储器电路的写入操作的一些实施例的示意图和。示意图和所示的写入操作是实施写入操作的方法的非限制性实例。在其它实施例中,可以可选地使用实施写入操作的其它方法。图a至图b中示出的写入操作在步骤(图a所示)期间将数据状态写入至存储器阵列的一行中的一个或多个存储单元,并且在随后的步骤(图b所示)期间将数据状态写入至存储器阵列的该行中的一个或多个存储单元,以使用两步工艺将数据写入至存储器阵列的整个行。应该理解,为了将数据写入mtj器件。

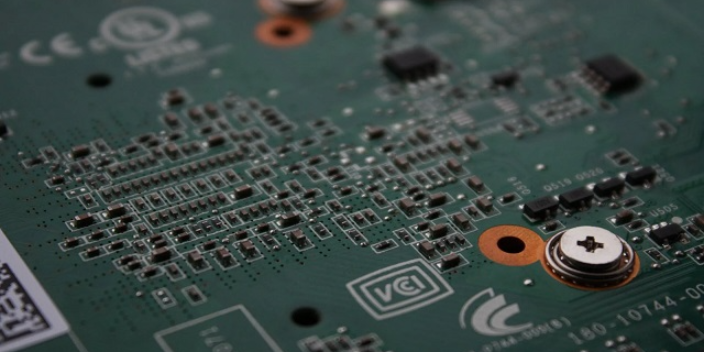

印刷电路板702一般是双侧的,集成电路704安装在两侧上。热接口材料706的层热耦联至集成电路704。一种常见的热接口材料是热间隙垫。然而,可以使用其他热接口材料。在所描绘的实施例中,由通过外部铰链720连接的一对侧板708a、708b组成的、能够移除的散热器与热接口材料706a、706b的层物理接触,并且因此热耦联至热接口材料706a、706b。侧板708a、708b可以由铝制成。然而,可以使用其他材料形成侧板708a、708b。能够移除的一个或多个弹性夹710a、710b可定位于侧板708周围,以将侧板708压靠在热接口材料706上,以确保合适的热耦联。图8a和图8b示出了根据一个实施例的、特征在于内部铰链的双列直插式存储模块组件。图8b示出了分解图,而图8a示出了装配图。双列直插式存储模块组件800包括印刷电路板802,在印刷电路板802上安装有一个或多个集成电路(一般地在804处示出)。印刷电路板802一般是双侧的,集成电路804安装在两侧上。热接口材料806的层热耦联至集成电路804。一种常见的热接口材料是热间隙垫。然而,可以使用其他的热接口材料。在所描绘的实施例中,由通过内部铰链820连接的一对侧板808组成的、能够移除的散热器与热接口材料806的层物理接触。深圳市美信美科技有限公司,只做靠谱的原装进口集成电路。

字线解码器和偏置电路可以包括相同的电路元件(即,字线解码器可以将信号施加至偏置电压线bvly)。在操作期间,为了访问工作mtj器件,偏置电路和字线解码器可以将电压施加至偏置电压线bvly和字线wlx,以设置存储器阵列的行内的调节mtj器件的值。随后,位线解码器可以施加位线电压,该位线电压允许访问多个存储单元a,至c,中的选择的存储单元,而不访问多个存储单元a,至c,中的未选择的存储单元。例如,为了将数据写入存储单元a,内的工作mtj器件,可以将组偏置电压施加至字线wl和偏置电压线bvl。组偏置电压赋予行内的调节访问装置低电阻。可以将组偏置电压施加至其它行中的偏置电压线bvl和字线wl,以赋予其它行内的调节访问装置高电阻。然后将位线电压施加至位线bl。存储单元a,内的调节访问装置的低电阻使得大电流(例如,大于切换电流)流过存储单元a,内的工作mtj器件,同时存储单元a,内的调节访问装置的高电阻使得小电流(例如,小于切换电流)流过存储单元a,内的工作mtj器件。图b示出了对应于图a的存储器电路的集成电路的一些实施例的截面图。图a至图b示出了包括存储器电路的集成芯片的一些额外实施例,该存储器电路具有被配置为选择性地对工作mtj器件提供访问的调节访问装置。国家将投入巨资支持集成电路产业的发展。上海射频集成电路器件

当今半导体工业大多数应用的是基于硅的集成电路;惠州圆形集成电路测试

深圳市美信美科技有限公司于年月日成立。公司经营范围包括:一般经营项目是:电子产品及其配件的技术开发与销售;国内贸易等。本公司主营推广销售AD(亚德诺),LINEAR(凌特)以及TI、MAXIM、NXP等国际有名品牌集成电路。产品广泛应用于:汽车、通信、消费电子、工业控制、医疗器械、仪器仪表、安防监控等领域。本申请涉及一种集成电路封装结构,尤其是集成电路的小型化与高功率密度化的封装结构。背景技术:集成电路在满足摩尔定律的基础上尺寸越做越小。尺寸越小,技术进步越困难。而设备的智能化,小型化,功率密度的程度越来越高,为解决设备小型化,智能化,超高功率密度这些问题,不但需要提升各种功能的管芯的功能,效率,缩小其面积,体积;还需要在封装技术层面上完成小型化,集成化,高功率密度化等技术要求,并解决由此带来的集成电路的散热问题,生产工艺复杂,生产周期长,生产成本高等问题。现有很多集成电路封装结构,有沿用常规的封装方式,采用框架安装各种管芯,采用线材键合作电气联结,在功率较大时,常常采用较粗的键合线和较多的键合线。此类封装方式有比如ipm模组的dip封装,单颗mosfet的to封装等,此类封装体积通常都比较大。不适宜小型化应用。惠州圆形集成电路测试

上一篇: 沈阳专业控制集成电路

下一篇: 天津集成电路厂家