福州PCIE分析仪费用

内存深度设置为总采集内存的1/2。所有盒对都可用于采集数据。如果选择整个内存,则要用于时间标签存储的默认Pod是左边的盒对,但未分配总线或信号的任何Pod都是可以使用的。跳变定时模式,时间标签存储需要1个Pod或1/2的采集内存:跳变时序采样模式也需要时间标签存储。当选择小采样周期时,必须将一个Pod对保留用于时间标签存储。在这种情况下,不能使用1/2(或更少)的模块采集内存来替代该Pod。对于其他采样周期,内存深度和通道数的权衡与状态采样模式下的相同。也就是说,要使用1/2以上的模块采集内存,必须将一个Pod保留用于时间标签存储。要使用所有Pod,内存使用量不能超过模块采集内存的1/2。一般来说,可用定时器数与那些不属于为时间标签存储而保留的Pod数相同。状态模式采样位置、眼定位和眼图扫描同步采样(状态模式)逻辑分析仪与触发时钟沿的触发相似,因为它们都需要输入逻辑信号才可以在时钟事件前(建立时间)和时钟事件后(保持时间)的一段时间内保持稳定,以便正确解释逻辑电平。组合建立和保持时间被称为建立/保持窗口。被测设备(由于其本身的建立/保持要求)可指定数据在某段时间内在总线上有效。这被称为数据有效窗口。一般情况下。100BaseTl (Automotive)协议分析仪/训练器找欧奥!福州PCIE分析仪费用

将内存深度设置为值的一半(或更小)将返回Pod。在状态采样模式中,在选择了高速状态模式采样选项的情况下,会将一个Pod对保留用于时间标签存储。在定时采样模式中,在选择了跳变/存储限定定时模式采样选项的情况下:选择了小采样周期时,会将一个Pod对保留用于时间标签存储。选择了除小采样周期之外的采样周期时,选择采集内存深度需要将一个Pod对保留用于时间标签存储。在这种情况下,将内存深度设置为值的一半(或更小)将返回Pod。该模块是已分离的逻辑分析仪的一部分。在这种情况下,Pod位于分离分析仪的另一半模块中。状态模式和跳变定时模式下通道数、内存深度和触发之间的相互影响:状态采样模式时,时间标签存储需要1个Pod或1/2的采集内存。在操作界面应用程序中,所有模块都与时间相关;不能关闭timetagstorage(时间标签存储)(虽然以前的Agilent逻辑分析系统可以)。要使用1/2以上的模块采集内存,必须将一个Pod保留用于时间标签存储。要使用所有Pod,内存使用量不能超过模块采集内存的1/2。一般来说,可用定时器数与那些不属于为时间标签存储而保留的Pod数相同。默认设置:时间标签存储始终处于开启状态(并且不能将其关闭)。肇庆分析仪价格协议分析仪/训练器厂家直销就找欧奥!

或称为逻辑分析系统),以16900系列逻辑分析系统为例,对应关系如下:插槽从上到下以A至F字母命名。有一条标有Pod2的电缆连接着每一个逻辑分析仪模块。知道某个Pod连接到哪个插槽很重要,因为如果在插槽A和B中都有逻辑分析仪模块,则将有两条盒电缆标有Pod2,但操作界面应用程序会把一条记作SlotAPod2,把另一条记作SlotBPod2。分清这两条电缆很重要。SlotAPod2等于PodA2。A2与SlotAPod2可互相替代;同样,D1与SlotDPod1也可互相替代。时钟Pod(ClockPod)由模块中所有Pod的所有时钟通道组成。每个Pod各有一个时钟通道。所有时钟通道按Clk1、Clk2、Clk3等进行编号。如果某逻辑分析仪模块有两个逻辑分析仪卡,每卡有四个Pod,则该逻辑分析仪的时钟通道标记为Clk1至Clk8。除了Clk1外,时钟通道还可标记为C1。C1和Clk1是一样的。在16900系列逻辑分析系统中,请勿混淆时钟通道C2与SlotC中的Pod2,后者记作PodC2。对于时钟通道,C是Clock的缩写,不是SlotC的缩写。为什么有时Pod会丢失?导致所有Pod对逻辑分析仪模块均不可用的原因有多种:在状态采样模式中,在选择了一般状态模式采样选项的情况下,选择采集内存深度需要将一个Pod对保留用于时间标签存储。在这种情况下。

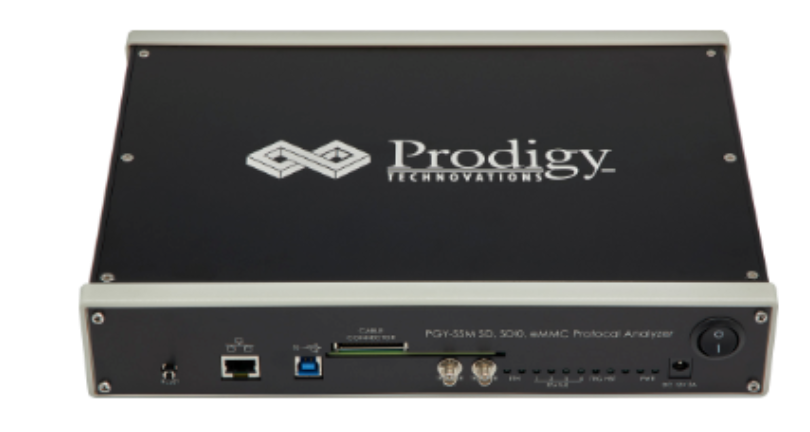

欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。时序和协议是数字系统调试的两大关键点,也是逻辑分析仪能发挥价值的地方。如何使用逻辑分析仪快速地完成接线配置并采集到数据呢?本文以IIC协议为例为大家实测演示。数字系统逻辑关系是通讯研发过程中的关键,它直接影响到整个设备系统能否正常工作。虽然示波器也能做部分数字信号分析,但受限于通道数(一般只有4个通道)和存储深度(较小)。逻辑分析仪可以达到34通道,记录深度长可达2G,再配合数据压缩算法,提高了工程师测试时序分析的效率。下面以IIC为例,分享逻辑分析仪测试步骤。一、准备工作测试主要为被测对象、逻辑分析仪、电脑,IIC协议信号。训练器哪家强?欧奥强!

同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。触发前获得/显示的样本数量在不同的测量中会有所变化。状态分析状态分析仪需要来自被测设备的采样时钟信号。这种类型的时钟计时可使逻辑分析仪中的数据采样与被测设备中的计时事件同步。具体来讲:状态分析仪适用于显示“有效时钟或控制信号”期间的信号活动是“什么”。状态分析仪侧重于查看指定执行时间内的信号活动,而不是与时序无关的信号活动。这就是为什么状态分析仪需要对与被测设备时钟信号“同步化”或同步的数据进行采样。对于微处理器,数据和地址可以出现在相同的信号线上。要采集正确的数据,逻辑分析仪必须对数据采样加以限制,使之只在所需的数据有效并出现在信号线上时进行。为此,它会从相同的信号线上采集数据样本,但使用来自被测设备的不同采样时钟。示例:以下时序图表明。I2C/SPI协议分析仪/训练器找欧奥!长沙协议分析仪

SPMl协议分析仪/训练器找欧奥!福州PCIE分析仪费用

等在选择内存长度时的基准是"于我们即将观测的系统可以进行分割后的块的长度。测试夹具逻辑分析仪通过探头与被测器件连接,测试夹具起着很重要的作用,测试夹具有很多种,如飞行头和苍蝇头等。探头逻辑分析仪通过探头与被测器件连接,探头起着信号接口的作用,在保持信号完整性中占有重要位置。逻辑分析仪与数字示波器不同,虽然相对上下限值的幅度变化并不重要,但幅度失真一定会转换成定时误差。逻辑分析仪具有几十至几百通道的探头其频率响应从几十至几百MHz,保证各路探头的相对延时小和保持幅度的失真较低。这是表征逻辑分析仪探头性能的关键参数。Agilent公司的无源探头和Tektronix公司的有源探头具代表性,属于逻辑分析仪的探头。逻辑分析仪的强项在于能洞察许多信道中信号的定时关系。可惜的是,如果各个通道之间略有差别便会产生通道的定时偏差,在某些型号的逻辑分析仪里,这种偏差能减小到小,但是仍有残留值存在。通用逻辑分析仪,如Tektronix公司的TLA600型或Agilent公司的HP16600型,在所有通道中的时间偏差约为1ns。因而探头非常重要,详见本站"测试附件及连接探头"。a、探头的阻性负载,也就是探头的接入系统中以后对系统电流的分流作用的小,在数字系统中。福州PCIE分析仪费用

上一篇: 梅州I2C/SPI分析仪

下一篇: 温州SD分析仪电话