广州PCIE分析仪找哪家

写入地址0x00,数据0x10,0x27等。由于写入以字节为单位,因此0x2710=10000,表明采样成功。将鼠标放在波形上,点击左键,实现zoomin功能。结果见图3,在“start”条件后,在SCL的8个连续脉冲的高电平处,SDA对应的信号为10100010,即0xA2,第9个脉冲高电平处为0,是ACK标志。以上简单介绍了用逻辑分析仪进行I2C分析的过程,可以看到操作起来非常简单。下面再介绍利用逻辑分析仪采样三相交流电机驱动器的6路PWM波形。硬件连接1.?先将逻辑分析仪的GND与目标板的GND连接,让二者共地,见图5。2.?选择需要采样的信号,这里就是单片机6路PWM波形的输出引脚,将其接入逻辑分析仪的通道1(Input1)至通道6(Input6),并且把通道的名字改为Utop、Ubottom、Vtop、Vbottom、Wtop、WBottom,分别三路输出的上下桥臂。3.?将逻辑分析仪和电脑USB口连接,windows会识别该设备,并在屏幕右下角显示USB设备标识。软件使用1.?运行Saleae软件,此时逻辑分析仪的硬件已经与电脑相连,软件会显示[Connected]。2.?设置采样数量和速度,PWM的频率为15kHz,这里设置为2MSamples@4MHz的速度。3.?设置触发条件,默认“----”就可以了。4.?按“start”按钮,开始采样。数据分析采样结束后。USB PD,3.1, 3.0,2.0协议分析仪/训练器找欧奥!广州PCIE分析仪找哪家

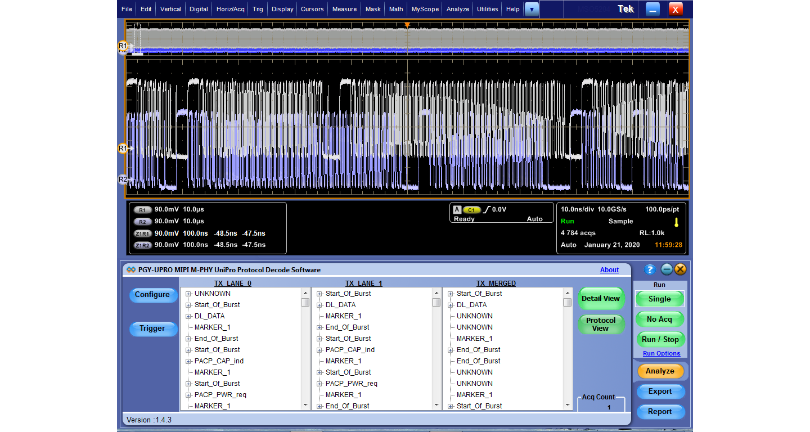

终比较结果将对“差分信号高于Vref还是低于Vref?”的问题作出解答:对眼隙的eyescan测量是通过使用不同Vref设置进行一系列eyefinder测量完成的。差分信号的默认eyefinder测量使用Vref=0V。通过将Vref增至零以上。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号。如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。我们会找到信号与上升的Vref值交叉的位置。如果Vref升至足够高,信号的顶部轨迹将通过Vref,我们便会看到眼的顶端。再将Vref升高一点会导致Vcomp保持在Vlo,表示信号不会升至该电之,将Vref移至零以下会看到眼的下半部。eyescan/eyefinder显示窗口会在每个信号的eyescan图下方显示eyefinder交叠部分,以此显示eyefinder与eyescan之间的这一关系。清远I2C/SPI分析仪价格训练器就找欧奥电子。

欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。时序和协议是数字系统调试的两大关键点,也是逻辑分析仪能发挥价值的地方。如何使用逻辑分析仪快速地完成接线配置并采集到数据呢?本文以IIC协议为例为大家实测演示。数字系统逻辑关系是通讯研发过程中的关键,它直接影响到整个设备系统能否正常工作。虽然示波器也能做部分数字信号分析,但受限于通道数(一般只有4个通道)和存储深度(较小)。逻辑分析仪可以达到34通道,记录深度长可达2G,再配合数据压缩算法,提高了工程师测试时序分析的效率。下面以IIC为例,分享逻辑分析仪测试步骤。一、准备工作测试主要为被测对象、逻辑分析仪、电脑,IIC协议信号。

如果在时钟沿检测器重置之前出现第二个时钟沿(在个时钟沿后),为避免数据丢失需要两个样本。在跳变定时中,每个序列步骤只有2个分支。在跳变时序中,只有一个全局计数器可用。跳变时序需要有时间标签才能重建数据。通过将时间标签与内存中的测量数据交叉可存储时间标签。默认情况下,分析仪将查找为逻辑分析仪模块定义的所有总线/信号上的转变。但是,为增加可用内存深度和采集时间,可以在高级触发中选择不存储某些总线/信号转变(如将无用信息添加到测量中的时钟或选冲信号)。运行测量时,无论总线/信号是否定义或是否分配给逻辑分析仪通道,都将在所有这些通道上采集数据。在跳变时序模式中,如果定义的总线/信号(未排除的)上存在转变,将保存采集的样本。运行跳变时序测量后,如果为以前未分配的逻辑分析仪通道定义新的总线/信号,那么将显示在这些通道上采集的数据,但是不可能存储这些总线/信号上的所有转变;显示的数据好似新的总线/信号在运行测量前就已经被排除了。在跳变时序中,不需要预先存储数据(触发前获得的样本)。因此,与状态模式非常相似的是,触发位置(起始/中心/结束)表明触发后样本占用内存的百分比。UFS协议分析仪/训练器找欧奥!

RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。内存深度设置为总采集内存的1/2。所有盒对都可用于采集数据。如果选择整个内存,则要用于时间标签存储的默认Pod是左边的盒对,但未分配总线或信号的任何Pod都是可以使用的。跳变定时模式,时间标签存储需要1个Pod或1/2的采集内存:跳变时序采样模式也需要时间标签存储。当选择小采样周期时。必须将一个Pod对保留用于时间标签存储。在这种情况下,不能使用1/2(或更少)的模块采集内存来替代该Pod。对于其他采样周期,内存深度和通道数的权衡与状态采样模式下的相同。也就是说,要使用1/2以上的模块采集内存,必须将一个Pod保留用于时间标签存储。要使用所有Pod,内存使用量不能超过模块采集内存的1/2。一般来说,可用定时器数与那些不属于为时间标签存储而保留的Pod数相同。状态模式采样位置、眼定位和眼图扫描同步采样(状态模式)逻辑分析仪与触发时钟沿的触发相似,因为它们都需要输入逻辑信号才可以在时钟事件前。SD协议分析仪/训练器厂家那家好?找欧奥!苏州协议分析仪那家好

HSIC协议分析仪/训练器找欧奥!广州PCIE分析仪找哪家

简单触发示例:请看下面显示的“D”触发器,在正值的时钟沿出现之前,“D”输入上的数据是无效的。因此,时钟输入为上限时,触发器的状态才有效。图8D触发器现在,假设我们有并行的八个此类触发器。如下所示,这八个触发器都连接到同一时钟信号。图9接收器当时钟线上出现高电平时,所有这八个触发器都会在其“D”输入处采集数据。此外,每次时钟线上出现正电平时都会发生有效状态。下面的简单触发指示分析仪在时钟线上出现高电平时在D0-D7这几条上收集数据。图10总线收集的数据高级触发示例:假设想查看地址值为406F6时内存中存储了哪些数据。对高级触发进行配置,以在地址总线上查找码型406F6(十六进制)以及在RD(内存读取)时钟线上查找高电平。图11高级触发设置在配置EdgeAndPatterntrigger(时钟沿和码型触发)对话框时,尝试将该操作看作是构造从左向右读取的句子。Pod、通道和时间标签存储Pod和通道的命名约定:Pod是一组逻辑分析仪通道的组合,共有17个通道,其中数据16个通道,时钟1个通道。逻辑分析仪的通道数是Pod数的倍数关系。34通道的逻辑分析仪对应两个Pod,68通道逻辑分析仪对应4个Pod,136通道逻辑分析仪对应8个Pod。对于模块化的逻辑分析仪。广州PCIE分析仪找哪家

上一篇: 汕尾RFFE分析仪收费

下一篇: 黄石分析仪找哪家