湛江UFS分析仪那家好

才能解决速度不够和通道数量不足的问题。图2图3图4下面就以Saleae逻辑分析仪为例,通过采样分析I2C总线波形和PWM波形,简单介绍它的特点和使用方法。先介绍用逻辑分析仪采样单片机对I2C器件AT24C16的写数据过程。硬件连接1.先将逻辑分析仪的GND与目标板的GND连接,让二者共地。2.选择需要采样的信号,这里就是AT24C16的SDA和SCL,将SDA接入逻辑分析仪的通道1(Input1),SCL接入通道1(Input2)。3.将逻辑分析仪和电脑USB口连接,windows会识别该设备,并在屏幕右下角显示USB设备标识。软件使用1.运行Saleae软件,此时逻辑分析仪的硬件已经与电脑相连,软件会显示[Connected]。2.设置采样数量和速度,I2C为低速通信,所以速度设置不必太高,这里设置为20MSamples@4MHz的速度,也就是能持续采样5秒钟。3.设置协议,点右上角的“Options”按钮,找到analyzer1,设置为I2C协议,详见图1。4.按“Start”按钮,开始采样。图5图6数据分析采样结束后,可以看到波形,见图2。由于我们设置了是I2C分析,因此不光显示出波形,还有根据I2C协议解码显示的字节内容。单片机对AT24C16进行写入操作,在0x00地址处写入10000等数字。波形起始是“start”信号,然后依次是AT24C16的标识0xA2。RFFE协议分析仪/训练器找欧奥!湛江UFS分析仪那家好

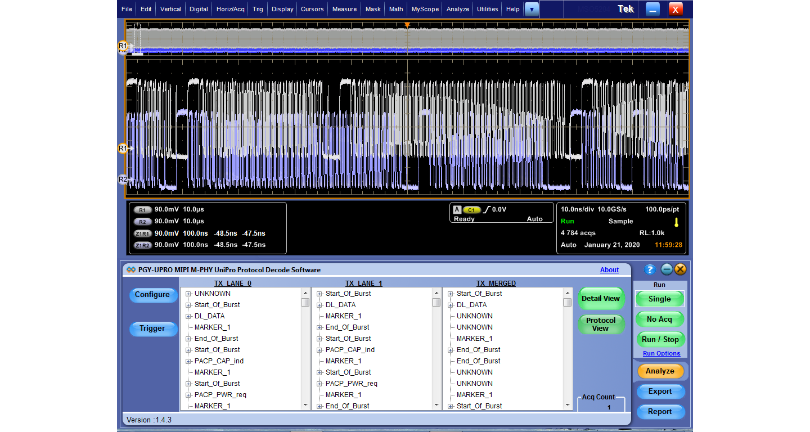

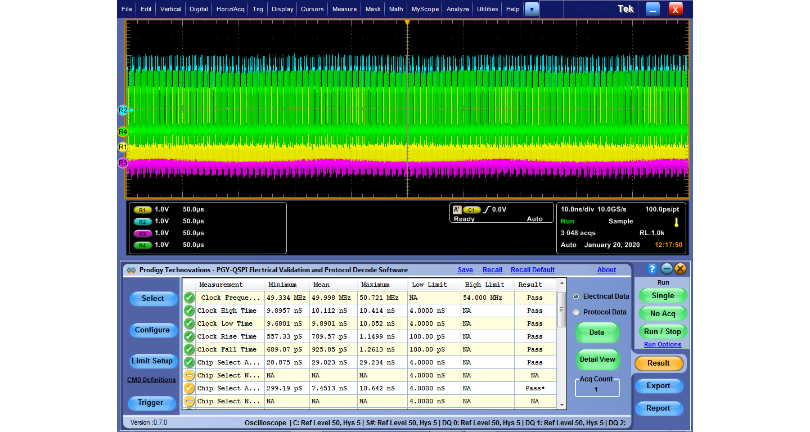

要采集地址,分析仪需要在MREQ线下降时进行采样。要采集数据,分析仪需要在WR线下降(写周期)或RD线下降(读周期)时进行采样。图7状态采集触发状态分析仪:与定时分析仪相似,状态分析仪也具有限定要存储的数据的功能。如果我们正在查找地址总线的上限和下限的特定码型,当分析仪找到该码型时,我们可以通知分析仪开始存储,并且只要分析仪的内存未满就一直存储。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪。包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。简单触发示例:请看下面显示的“D”触发器,在正值的时钟沿出现之前,“D”输入上的数据是无效的。因此,时钟输入为上限时,触发器的状态才有效。图8D触发器现在,假设我们有并行的八个此类触发器。如下所示。连云港SDIO分析仪收费eMMC协议分析仪/训练器找欧奥!

但由于“转到”操作,剩余的序列步骤可以以任意顺序执行。执行一个序列步骤且布尔逻辑表达式均为假时,逻辑分析仪将采集下一样本并再次执行同一序列步骤于“KeepacquiringmoresamplesuntilDATA=7000,thentrigger”。如果符合一个序列步骤中的布尔逻辑表达式,那么在执行下一序列步骤之前总是采集另一样本。换句话说,如果一个样本符合序列步骤1的条件,在执行序列步骤2前将采集另一样本。这意味着一个单独的样本不可能符合多个序列步骤的条中的条件二者之间采集了新的样本,因此逻辑分析仪不会在采集样本#1时触发。可将此触发序列看作是“FindADDR=1000followedbyDATA=2000andthentrigger”。触发序列中的多序列步骤暗示了“后接”。逻辑分析仪触发后,将不会再次触发。换句话说。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。

以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。没有额外的被测设备)的一小段时间内,可以自动:定位每个通道上的建立/保持窗口。针对尽可能宽的数据有效窗口调整阈电压设置。眼定位是获得尽可能小的逻辑分析仪建立/保持窗口的一种简单方法。眼定位概要:对于指定的状态采样时钟,眼定位可在时钟沿前后的一个固定时间范围内查找数据信号转变(阈电压交叉点),并为显示相关内容以帮助设置佳采样位置。为了了解眼定位显示,需为每个活动时钟沿拍摄一张有关该时钟沿的数据信号转变的“照片”。将此照片看作快照、定格画面或频闪观测仪(位于时钟沿中心或与时钟沿同步)。到达时钟沿的时间为T=0。例如,如果选择盒1上时钟输入的上升沿作为状态采样时钟,每次拍摄“照片”时,都将达到盒1时钟上的上升沿。盒1时钟沿之间的时间是否相同无关紧要。如果同时在上升沿和下降沿上进行采样,那么在每一个时钟沿上都会拍摄一张“照片”。此外,在活动沿之间消耗了多少时间也不重要。每一个时钟沿上都要拍摄“照片”。要构建眼定位显示。I3C协议分析仪/训练器找欧奥!

系统的电流负载能力一般在几个KΩ以上,分流效应对系统的影响一般可以忽略,现在流行的几种长逻辑分析仪探头的阻抗一般在20~200KΩ之间。b、探头的容性负载:容性负载就是探头接入系统时,探头的等效电容,这个值一般在1~30PF之间,在高速系统中,容性负载对电路的影响远远于阻性负载,如果这个值太,将会直接影响整个系统中的信号"沿"的形状改变整个电路的性质,改变逻辑分析仪对系统观测的实时性,导致我们看到的并不是系统原有的特性。c、探头的易用性:是指探头接入系统时的难易程度,随着芯片封装的密度越来越高,出现了BGA、QFP、TQFP、PLCC、SOP等各种各样的封装形式,IC的脚间距小的已达到,要很好的将信号引出,特别是BGA封装,确实有困难,并且分立器件的尺寸也越来越小,典型的已达到×。d、与现有电路板上的调试部分的兼容性。6、系统的开放性:随着数据共享的呼声越来越高,我们所使用的系统的开放性就越来越重要,逻辑分析仪的操作系统也由过去的系统发展到使用Windows介面,这样我们在使用时很方便。小结如果在你的工作中有数字逻辑信号,你就有机会使用逻辑分析仪。因此应选好一种逻辑分析仪,既符合所用的功能,又不太超越所需的功能。HSIC协议分析仪/训练器找欧奥!重庆分析仪品牌

SMI(MDIO)协议分析仪/训练器找欧奥!湛江UFS分析仪那家好

DampedResistorProbing),电阻匹配探测(ResistiveDividerProbing)。短线探测会增加电容负载。举例:探头电容负载是,连接短线是50欧姆微带线(C=3pF/in),长度1英寸。则整个探头的电容负载是,这个短线是电容负载的主要部分。被测系统可容忍的负载电容是多少呢?需要参考被测电路的系统上升时间,一般规则:短线的电气长度<>PCB传输延迟:150ps/in系统上升时间:500ps则电气长度:则短线长度:(100ps)/(150ps/in)=。如果没法减小短线长度,可以试着用阻尼电阻探测的方式。阻尼电阻有2个作用:隔离来自短线的电容,消减来自短线的反射。图25阻尼电阻探测方式阻尼电阻阻值小的一般规则:目标阻抗的。如果探测环境需要更长的连线,这时候可考虑电阻匹配探测,即在探头尖处附加一个匹配电阻,消除连线的反射。匹配电阻的阻值与连线传输线的阻抗一样即可,但需要考虑信号的衰减。图26电阻匹配探测方式逻辑分析仪的探头主要有3种类型:提前设计型;事后考虑型;定制型。图27逻辑分析仪的探头类型小结:逻辑分析仪探头是逻辑分析仪非常重要的部分,典型探头的形状,连接,参数如下图所示。湛江UFS分析仪那家好

上一篇: 常州I3C分析仪找哪家

下一篇: 杭州UFS分析仪售价