NC7SZ32L6X

集成电路发展对策建议:创新性效率超越传统的成本性静态效率,从理论上讲,商务成本属于成本性的静态效率范畴,在产业发展的初级阶段作用明显。外部商务成本的上升实际上是产业升级、创新驱动的外部动力。作为高新技术产业的上海集成电路产业,需要积极利用产业链完备、内部结网度较高、与全球生产网络有机衔接等集群优势,实现企业之间的互动共生的高科技产业机体的生态关系,有效保障并促进产业创业、创新的步伐。事实表明,20世纪80年代,虽然硅谷的土地成本要远高于128公路地区,但在硅谷建立的半导体公司比美国其他地方的公司开发新产品的速度快60%,交运产品的速度快40%。具体而言,就是硅谷地区的硬件和软件制造商结成了紧密的联盟,能至大限度地降低从创意到制造出产品等相关过程的成本,即通过技术密集关联为基本的动态创业联盟,降低了创业成本,从而弥补了静态的商务成本劣势。集成电路的不断发展和创新带来了数字电子产品的高速、低功耗和成本降低等优势。NC7SZ32L6X

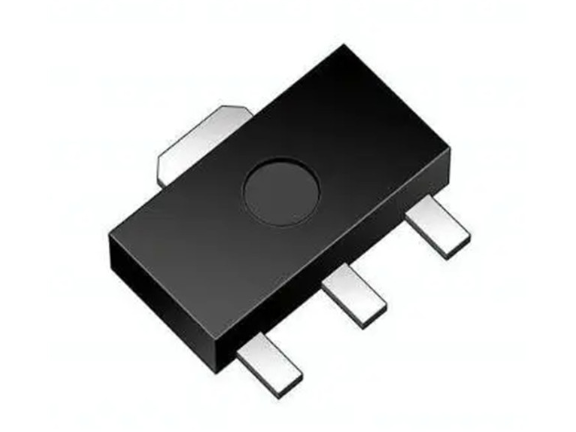

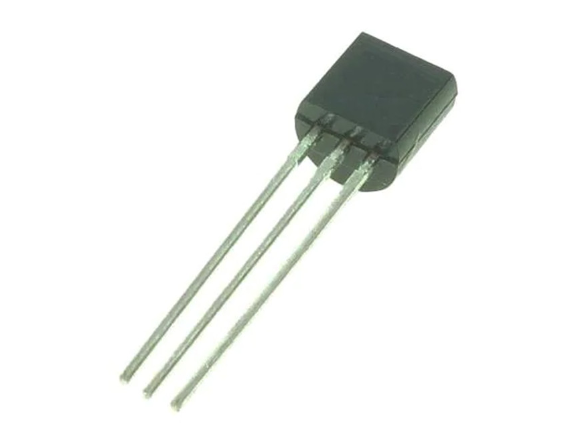

在光刻工艺中,首先需要将硅片涂上一层光刻胶,然后使用光刻机将光刻胶暴露在紫外线下,形成所需的图案。接着,将硅片放入显影液中,使未暴露的光刻胶被溶解掉,形成所需的图案。通过将硅片放入蚀刻液中,将暴露出来的硅片部分蚀刻掉,形成所需的电路结构。光刻工艺的精度和稳定性对电路的性能和可靠性有着重要的影响。外延工艺是集成电路制造中用于制备复杂器件的重要工艺之一,其作用是在硅片表面上沉积一层外延材料,以形成复杂的电路结构和器件。外延材料可以是硅、砷化镓、磷化铟等半导体材料。在外延工艺中,首先需要将硅片表面清洗干净,然后将外延材料沉积在硅片表面上。外延材料的沉积过程需要控制温度、压力和气体流量等参数,以保证外延层的质量和厚度。外延工艺的精度和稳定性对电路的性能和可靠性有着重要的影响。外延工艺还可以用于制备光电器件、激光器件等高级器件,具有普遍的应用前景。CD4049UBCMX集成电路的封装外壳多样化,圆壳式、扁平式和双列直插式是常见的形式。

集成电路是指将多个电子元器件集成在一起,形成一个完整的电路系统。它的高集成度是指在一个芯片上集成了大量的电子元器件,从而实现了高度的集成化。这种高度的集成化不仅可以很大程度上减小电路的体积,还可以提高电路的可靠性和稳定性。此外,高集成度还可以降低电路的功耗,提高电路的效率。因此,集成电路的高集成度是现代半导体工业主流技术的重要特点之一。集成电路的高集成度可以带来许多好处。首先,它可以很大程度上减小电路的体积,从而使得电子设备更加轻便、便携。其次,高集成度可以提高电路的可靠性和稳定性,减少故障率,延长电子设备的使用寿命。此外,高集成度还可以降低电路的功耗,提高电路的效率,从而使得电子设备更加节能环保。因此,集成电路的高集成度是现代半导体工业主流技术的重要特点之一。

制作工艺:集成电路按制作工艺可分为半导体集成电路和膜集成电路。膜集成电路又分类厚膜集成电路和薄膜集成电路。集成电路按导电类型可分为双极型集成电路和单极型集成电路,他们都是数字集成电路。双极型集成电路的制作工艺复杂,功耗较大,按用途:集成电路按用途可分为电视机用集成电路、音响用集成电路、影碟机用集成电路、录像机用集成电路、电脑(微机)用集成电路、电子琴用集成电路、通信用集成电路、照相机用集成电路、遥控集成电路、语言集成电路、报警器用集成电路及各种集成电路。集成电路技术的不断创新和突破,为电子产品的功能丰富化提供了强大支持。

各楼层直接有高速电梯可达,为了效率和功能隔离,还可能有多部电梯,每部电梯能到的楼层不同——这是集成电路的布线,电源线、地线单独走线,负载大的线也宽;时钟与信号分开;每层之间布线垂直避免干扰;CPU与存储之间的高速总线,相当于电梯,各层之间的通孔相当于电梯间……集成电路或称微电路(microcircuit)、微芯片(microchip)、芯片(chip)在电子学中是一种把电路(主要包括半导体装置,也包括被动元件等)小型化的方式,并通常制造在半导体晶圆表面上。为了支持集成电路产业的发展,可以通过持续支持科技重大专项、加大产业基金投入等措施来推动行业发展。MBR60L45CTG

集成电路的器件设计考虑到布线和结构的需求,如折叠形状和叉指结构的晶体管等,以优化性能和降低尺寸。NC7SZ32L6X

尽管随机存取存储器结构非常复杂,几十年来芯片宽度一直减少,但集成电路的层依然比宽度薄很多。组件层的制作非常像照相过程。虽然可见光谱中的光波不能用来曝光组件层,因为他们太大了。高频光子(通常是紫外线)被用来创造每层的图案。因为每个特征都非常小,对于一个正在调试制造过程的过程工程师来说,电子显微镜是必要工具。在使用自动测试设备(ATE)包装前,每个设备都要进行测试。测试过程称为晶圆测试或晶圆探通。晶圆被切割成矩形块,每个被称为“die”。每个好的die被焊在“pads”上的铝线或金线,连接到封装内,pads通常在die的边上。封装之后,设备在晶圆探通中使用的相同或相似的ATE上进行终检。测试成本可以达到低成本产品的制造成本的25%,但是对于低产出,大型和/或高成本的设备,可以忽略不计。在2005年,一个制造厂(通常称为半导体工厂,常简称fab,指fabrication facility)建设费用要超过10亿美金,因为大部分操作是自动化的。NC7SZ32L6X

上一篇: 1SMA5921BT3G

下一篇: NC7SZ384P6X