绝缘体上硅键合机三维芯片应用

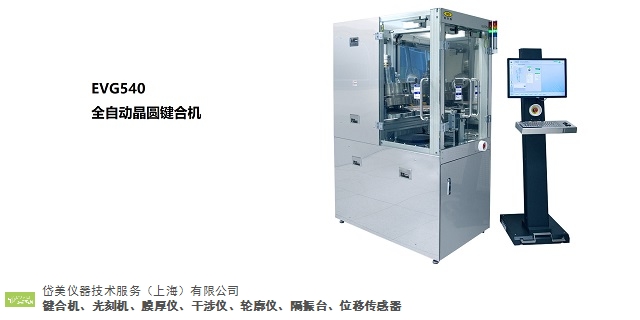

长久键合系统 EVG晶圆键合方法的引入将键合对准与键合步骤分离开来,立即在业内掀起了市场geming。利用高温和受控气体环境下的高接触力,这种新颖的方法已成为当今的工艺标准,EVG的键合机设备占据了半自动和全自动晶圆键合机的主要市场份额,并且安装的机台已经超过1500个。EVG的晶圆键合机可提供蕞/佳的总拥有成本(TCO),并具有多种设计功能,可优化键合良率。针对MEMS,3D集成或gao级封装的不同市场需求,EVG优化了用于对准的多个模块。下面是EVG的键合机EVG500系列介绍。 晶圆键合系统EVG501可以用于学术界和工业研究。绝缘体上硅键合机三维芯片应用

阳极键合是晶片键合的一种方法,广FAN用于微电子工业中,利用热量和静电场的结合将两个表面密封在一起。这种键合技术ZUI常用于将玻璃层密封到硅晶圆上。也称为场辅助键合或静电密封,它类似于直接键合,与大多数其他键合技术不同,它通常不需要中间层,但不同之处在于,它依赖于当离子运动时表面之间的静电吸引对组件施加高电压。可以使用阳极键合将金属键合到玻璃上,并使用玻璃的薄中间层将硅键合到硅上。但是,它特别适用于硅玻璃粘接。玻璃需要具有高含量的碱金属(例如钠),以提供可移动的正离子。通常使用一种特定类型的玻璃,其中包含约3.5%的氧化钠(Na2O)。 氮化镓键合机自动化测量晶圆键合系统EVG501是适用于学术界和工业研究的多功能手动晶圆键合设备。

共晶键合[8,9]是利用某些共晶合金熔融温度较低的特点,以其作为中间键合介质层,通过加热熔融产生金属—半导体共晶相来实现。因此,中间介质层的选取可以很大程度影响共晶键合的工艺以及键合质量。中间金属键合介质层种类很多,通常有铝、金、钛、铬、铅—锡等。虽然金—硅共熔温度不是蕞 低( 363 ℃ ) 的,但其共晶体的一种成分即为预键合材料硅本身,可以降低键合工艺难度,且其液相粘结性好,故本文采用金—硅合金共晶相作为中间键合介质层进 行表面有微结构的硅—硅共晶键合技术的研究。而金层与 硅衬底的结合力较弱,故还要加入钛金属作为黏结层增强金层与硅衬底的结合力,同时钛也具有阻挡扩散层的作用, 可以阻止金向硅中扩散[10,11]。

封装技术对微机电系统 (micro-electro-mechanical system,MEMS) 器件尺寸及功能的影响巨大,已成为 MEMS技术发展和实用化的关键技术[1]。实现封装的技术手段很多,其中较关键的工艺步骤就是键合工艺。随着 MEMS 技术的发展,越来越多的器件封装需要用到表面带有微结构的硅片键合,然而MEMS器件封装一般采用硅—硅直接键合( silicon directly bonding,SDB) 技术[2]。由于表面有微结构的硅片界面已经受到极大的损伤,其平整度和光滑度远远达不到SDB的要求,要进行复杂的抛光处理,这DADA加大了工艺的复杂性和降低了器件的成品率[3]。 EVG键合机也可以通过添加电源来执行阳极键合。对于UV固化的黏合剂,可选的键合室盖里具有UV源。

EVG501是一种高度灵活的晶圆键合系统,可处理从单芯片到150 mm(200 mm键合室的情况下为200 mm)的基片。该工具支持所有常见的晶圆键合工艺,如阳极,玻璃料,焊料,共晶,瞬态液相和直接键合。易于操作的键合室和工具设计,让用户能快速,轻松地重新装配不同的晶圆尺寸和工艺,转换时间小于5分钟。这种多功能性非常适合大学,研发机构或小批量生产。键合室的基本设计在EVG的HVM(量产)工具上是相同的,例如GEMINI,键合程序很容易转移,这样可以轻松扩大生产量。 键合机晶圆对准键合是晶圆级涂层,晶圆级封装,工程衬底智造,晶圆级3D集成和晶圆减薄等应用实用的技术。晶圆片键合机代理商

除了支持3D互连和MEMS制造,晶圆级和先进封装外,EVG的EVG500系晶圆键合机还可用于研发,中试和批量生产。绝缘体上硅键合机三维芯片应用

晶圆级封装的实现可以带来许多经济利益。它允许晶圆制造,封装和测试的集成,从而简化制造过程。缩短的制造周期时间可提高生产量并降低每单位制造成本。晶圆级封装还可以减小封装尺寸,从而节省材料并进一步降低生产成本。然而,更重要的是,减小的封装尺寸允许组件用于更广范的高级产品中。晶圆级封装的主要市场驱动因素之一是需要更小的组件尺寸,尤其是减小封装高度。岱美仪器提供的EVG的晶圆键合机,可以实现晶圆级封装的功能。 绝缘体上硅键合机三维芯片应用

上一篇: 吉林EVG850 TB键合机

下一篇: SOI键合机质量怎么样